1A/D转换器

出处:按学科分类—工业技术 北京出版社《现代综合机械设计手册下》第2777页(1927字)

A/D转换器的类型较多,如并联比较型、逐次逼近型等。并联比较型A/D转换器的电路结构如图8.3-73所示,包括分压器、比较器、编码器三部分。其中,分压器由基准电压源Us和八只相等的电阻R串联组成,每只电阻的压降为1/8Us。七个比较器的同相端都接输入模拟电压ux,反相端分别接分压器。ux的允许范围是0~Us,编码器把七个比较器的输出A、B、C、D、E、F、G译成三位二进制数码D2D1D0。并联比较型A/D转换器的优点是转换速度快,缺点是位数越多所需要的比较器数目越多。

图8.3-73 并联比较型A/D转换器

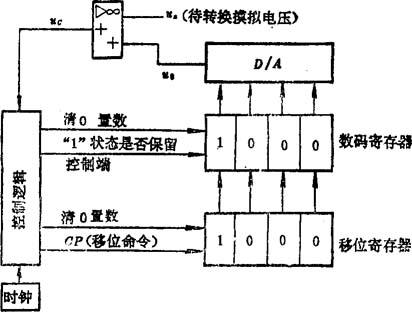

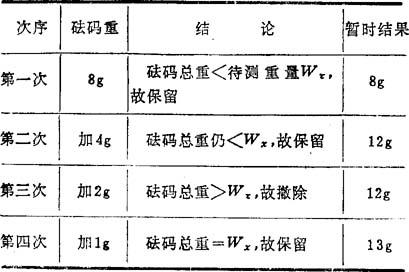

逐次逼近型A/D转换器的电路框图如图8.3-74所示.其工作原理可比喻为天平称重过程。例如,有8、4、2、1g四只砝码,设待称重量Wx=13g,则可用表8.3-57所示步骤称量。可以看出,称量过程遵循的规则是:1.按砝码重量逐次减半的顺序加入砝码。2.每次所加砝码是否保留,取决于加入新的砝码后天平上的砝码总重量是否超过待测重量。若超过,则应撤除新加入的砝码;若未超过,则保留新加砝码。3.重量最轻的砝码也试过后,则天平上所有砝码的重量总和就是待测物重量。

图8.3-74 逐次逼近型A/D转换器电路框图

表8.3-57 称重步骤

逐次逼近型A/D转换器的工作原理,与上述过程十分相似。转换前,先将各寄存器清0。转换开始后,先将移位寄存器最高位置1,并将此位1送入数码寄存器的相应位中,此时数码寄存器输出的数字量为1000,该数被D/A转换器转换成相应的模拟电压u0,送入比较器与待转换的模拟量ux相比较。若u0>ux,说明数字量大于待测量,故应将数码寄存器中最高位的1撤除。若u0<ux,说明数字量小于待测量,则应将这一位1保留。由于当u0>ux时,运放输出uc为高电平,即为1,否则为0。因此,可根据运放的输出状态经控制逻辑电路产生不同的控制信号,来控制数码寄存器中相应位的1应是保留或是撤除。

最高位比较过程完成后,移位寄存器中的1右移一位,然后将此位1送入数码寄存器的相应位中,并经同样的转换过程来确定该位的1是否应保留。如此逐位比较,直到最低位进行完毕为止。最后,数码寄存器中的存数就是ux转换成的数字量。

逐次逼近型A/D转换电路,就其构成来说比并联型A/D转换器节省器件,转换速度也不慢,因此应用较广泛。

A/D转换器的主要技术指标如下:

①分辨率——以输出二进制数的位数表示。位数越多,误差越小,转换精度越高。

②相对精度——实际转换值和理想特性之间的最大偏差。

③转换速度——完成一次A/D转换所需要的时间。低速的ADC为1~30ms,中速为50μs左右。高速约为50ns。

④电源抑制——转换电路的电源电压发生变化时,对输出产生的影响。这种影响,可用输出数字量的绝对变化量表示。

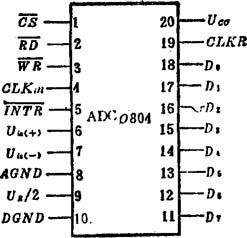

集成电路A/D转换组件有多种型号,如高速的、高分辨率的、高速高精度的等。例如,八位分辨率的模数转换芯片ADC0804,完成一次转换需100μs,转换精度为最低位的一个字。输入电压为0~5V,增加一定的外部电路后,输入模拟电压可为±5V。该芯片时钟脉冲CLK可由自身产生。 、

、 为低电平启动转换,转换结束时产生结束信号

为低电平启动转换,转换结束时产生结束信号 读取转换数据时,

读取转换数据时, 与

与 为低电平。ADC0804共有20个引出端,如图8.3-75所示。其中:Ucc为组件所需+5V电源;UR/2为组件内部电阻网络所用基准电源,其值约为输入电压范围的1/2(当输入电压为0~5V时,可由Ucc经内部分压得到,不需外接任何电源);DGND、AGND分别为数字地、模拟地;UiN(+)、UlN(一)为模拟输入端;D7~D0为信号输出端;CLKln为外部时钟输入端;

为低电平。ADC0804共有20个引出端,如图8.3-75所示。其中:Ucc为组件所需+5V电源;UR/2为组件内部电阻网络所用基准电源,其值约为输入电压范围的1/2(当输入电压为0~5V时,可由Ucc经内部分压得到,不需外接任何电源);DGND、AGND分别为数字地、模拟地;UiN(+)、UlN(一)为模拟输入端;D7~D0为信号输出端;CLKln为外部时钟输入端; 片选;

片选; 和

和 分别为写入和读出;

分别为写入和读出; 中断请求;CLKR为内时钟发生器外接电阻端。

中断请求;CLKR为内时钟发生器外接电阻端。

图8.3-75 ADC0804引出端