几种常用的组合逻辑部件

出处:按学科分类—工业技术 北京出版社《现代综合机械设计手册下》第2758页(1728字)

常用的组合逻辑部件有译码器、编码器、全加器和数字比较器等。

由输出的状态来表示输入代码的逻辑组合的数字电路,称为译码器,也叫解码器。根据其功能特点,可分成通用译码器及显示译码器两大类。国产通用译码器系列及其功能表(真值表)见表8.3-35和8.3-36。国产显示译码器系列及七段字形显示译码驱动器功能表见表8.3-37和8.3-38。

表8.3-35 国产通用译码器系列品种

注,①表示选通到输出。

②X/Y中,X表示地址到输出;Y表示选通到输出。

表8.3-36 通用译码器真值表

表8.3-37 显示译码器系列品种

表8.3-38 七段字形显示译码驱动器真值表

注:*T1049、T1048、T4048为“0编码是译码的逆过程。编码器的主要逻辑功能,是将电路的某种状态译成相应的代码。国产TTL编码器有两大类,共七个品种。其系列及真值表见表8.3-39和8.3-40。

表8.3-39 国产编码器系列品种

表8.3-40 编码器真值表

注:①T4348中S为E:“1”为“Z”

②YEx为优先扩展端。

图8.3-50 全加器逻辑符号

全加器逻辑符号如图8.3-50所示。它是被加数、加数以及低位的进位三者相加,故有三个输入端、两个输出端。设输入中的an为被加数、bn为加数、Cn-1为低位向本位的进位,输出中的Sn为本位和、Cn为本位向高位的进位,根据全加规则,则可写出全加逻辑状态表,见表8.3-41。根据逻辑状态表可分别写出输出端Sn和Cn的逻辑表达式为:

表8.3-41 全加器逻辑状态表

根据上述原理,可将多个全加器集成在同一芯片上,制成加法器集成电路组件。国产全加器型号及特点见表8.3-42。

表8.3-42 国产全加器型号及特点

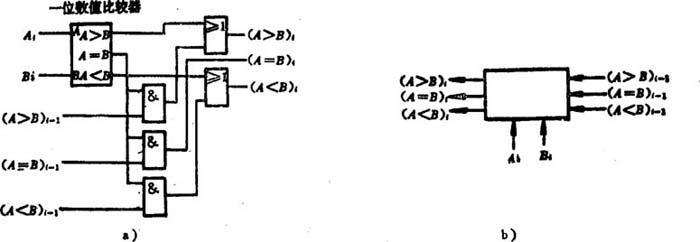

数字比较器简称比较器。一位数值比较器所实现的逻辑功能和逻辑符号分别如表8.3-43和图8.3-51所示。多位数值比较器中的某一位比较环节,应具有表8.3-44所示的逻辑功能,其原理电路及逻辑符号如图8.3-52所示。将多个典型比较环节集成到同一芯片上,即可构成中规模多位数字比较器集成组件。在中规模TTL集成电路中,具有较强比较功能的电路是四位数字比较器,见表8.3-45。

表8.3-43 一位数值比较器逻辑功能

图8.3-51 一位数值比较器逻辑符号

表8.3-44 多位数值比较器某一位的逻辑功能

注:①φ表示无所谓状态。

图8.3-52 多位数值比较器原理电路

表8.3-45 T1085、T3085、T4085功能表