典型的微处理器

出处:按学科分类—工业技术 企业管理出版社《工程师手册》第740页(4631字)

1.Intel 80386

80386是Intel公司推出的32位微处理器。

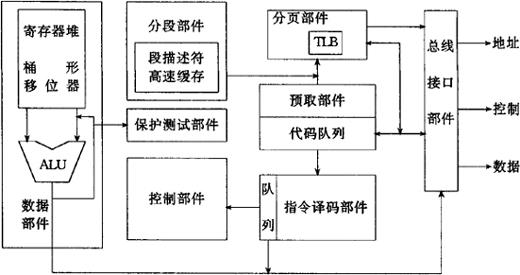

(1)80386的流水线结构 如图1.2.2-1所示,80386由总线接口部件、预取部件、指令译码部件、控制部件、数据部件、保护测试部件、分段部件、分页部件构成。

图1.2.2-1 80386的流水线结构

(2)80386的寄存器 80386共有34个寄存器,可分为通用寄存器、段寄存器、状态和控制寄存器、系统地址寄存器、调制寄存器、测试寄存器6类。

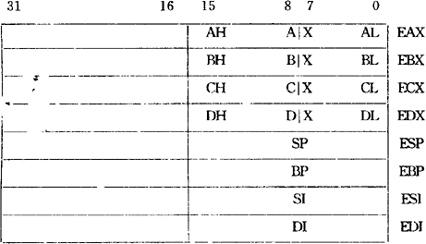

①通用寄存器 80386有8个32位的通用寄存器,如图1.2.2-2所示。

图1.2.2-2 80386的通用寄存器

EAX 累加器;

EBX 基地地寄存器;

ECX 计数寄存器;

EDX 数据寄存器;

ESP 堆栈指示器;

EBP 基地址指示器;

ESI 源变址寄存器;

EDI 目的变地寄存器。

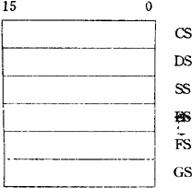

②段寄存器 80386有6个16位的段寄存器,如图1.2.2-3所示。

图1.2.2-3 80386的段寄存器

CS 指令码段寄存器;

DS 数据段寄存器;

SS 堆栈段寄存器;

ES 附加数据段寄存器;

FS 附加数据段寄存器;

GS 附加数据段寄存器。

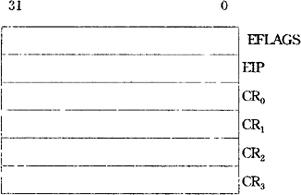

③状态和控制寄存器 包括1个标志寄存器EFLAGS、1个指令指示器EIP和4个控制寄存器TP0~TP3,如图1.2.2-4所示。均为32位的寄存器。

图1.2.2-4 80386的状态和控制寄存器

EFLAGS 标志寄存器,含以下13个标志。

CF 位0,进位标志;

AF 位2,奇偶标志;

PF 位4,辅助进位标志;

ZF 位6,零标志:

SF 位7,符号标志;

TF 位8,自陷标志;

IF 位9,允许中断标志;

DF 位10,方向标志;

OF 位11,溢出标志;

IOPL 位13、12,占2位,I/O特权标志;

NT 位14,嵌套任务标志;

RF 位16,恢复标志;

VM 位17,虚拟方式标志。

EIP 指令指示器,存放下一条要执行指令的偏移值。

TP0 机器状态字寄存器;

TP1 未定义,备用;

TP2 页故障线性地址寄存器;

TP3 页目录基址寄存器。

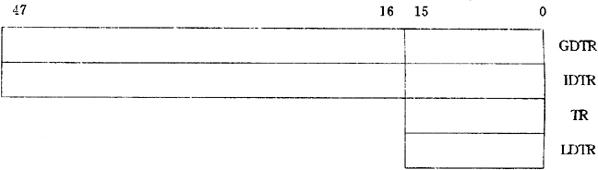

④系统地址寄存器 4个,分别为GDTR、IDTR、TR和LDTR,如图1.2.2-5所示。

图1.2.2-5 80386的系统地址寄存器

GDTR 全局描述符表寄存器,保存全局描述符表的32位线性地址和其16位界限;

TDTR 中断描述符表寄存器,保存中断描述符表的32位线性地址和其16位界限;

TR 任务状态寄存器,16位;

LDTR 局部描述符表寄存器.16位。

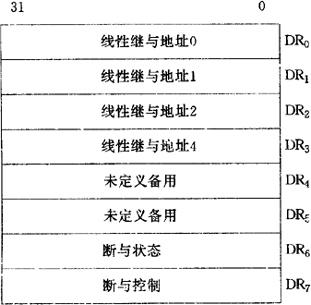

⑤调试寄存器 8个,DR0~DR7,均为32位,如图1.2.2-6所示。

图1.2.2-6 80386的调试寄存器

⑥测试寄存器 2个,TR6~TR7,均为32位,如图1.2.2-7所示。

图1.2.2-7 80386的测试寄存器

TR6 测试命令寄存器,存放测试控制命令;

TR7 数据寄存器,存放测试的数据。

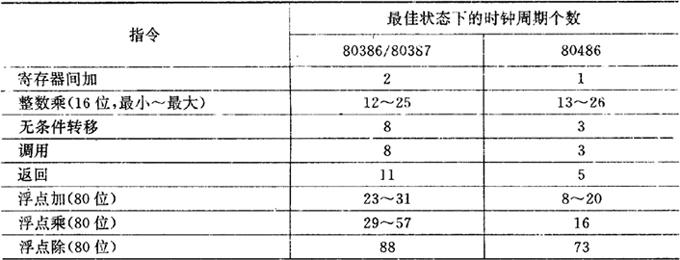

2.Inter80486

80486是Intel公司继80386推出的32位微处理器。其性能较80386有很大提高,具有小型计算机的某些特征。表1,2.2-1给出了80486与80386在一些指令的执行时间上的对比,可以看出,80486的执行速度比80386快2~3倍。

表1.2.2-1 80386与80486的指令执行时间对照

80486微处理器由主处理机部件、数值协同处理器部件和高速缓冲存储器部件(Cache)构成。其主处理机部件相当于提高了效率的80386微处理器,其数值协同处理器部件相当于增强了性能的80387数值协同处理器,其高速缓冲存储器部件是拥有8k字节的完整的Cache。在80386上,这3个部件各为一个芯片。在80486上,由于采用了先进的集成电路工艺,这3个部件集成在一个芯片上。

3.80586的改进

为了与RISC体系结构的微处理器进行市场竞争,586系列微处理器的体系结构设计对80486作了重大改进。这些改进可以归纳如下:

(1)586采用了RISC体系结构型CPU,并且其CPU采用超标量结构;

(2)586的浮点处理部件采用了超级流水线技术;

(3)586中增设了动态转移预测机构;

(4)586中在片Cache的复写操作,改用回写方式;

(5)586中增强了对错误检测和报告的功能;

(6)586采用了多种测试挂钩,例如边界扫描和探针方式等。

另外,在提高工作频率、固化指令、增加页码、增强微码等几个方面也作了改进。

(1)提高工作频率

目前486系列中工作频率最高者为486DX/50,其频率为50MHz。486DX2/50和486DX2/66内部工作频率为50MHz和66MHz,但由于采用的是倍速技术,其外部工作频率实际只有25MHz和33MHz。而586目前的两种型号586/60和586/66的内部频率和外部频率一致,分别达到60MHz和66MHz。频率加快,运算速度自然也得到提高。

(2)固化指令

在586中,常用指令MOV、ALU、INC、DEC、PUSH、POP、JMP、CALL(near)、NOP、SHIFT、ROT、NOT和TEST等改用硬性实现,不再使用微码操作,使指令的运行得到进一步加快。而其他的微码指令由于运行于双流水线上,速度也得到了提高。

(3)增加页尺寸

在586体系中,存储器中每一页的尽寸除与486兼容的4KB外,还多加了一种4MB。页尺寸的增加,使程序在搬动大的目标如图形Frame buffer时避免了频繁的换页操作。

(4)增强微码

586的内部总线同486一样为32位,但它通向存储器的外部数据总线为64位宽,在一个周期内,将数据传输量增加了一倍。586还支持多种类型的总周期,其中包括一种突发模式,该种模式下可以在一个总线周期装入256位数据。64位的数据总线使586与主存的数据交换速度达到528MB/s,为50MHz486(160MB/s)速度的3倍还多。

586的外部数据总线为64位,地址总线扩充到36位,藉以提高指今和数据的供给能力。外部总线宽度采用类似于RISC体系结构的64位结构,地址总线也扩充为36位,这是因为目前4GB大小的物理地址空间已不能满足要求所致。

586处理器的性能是在保持与80486兼容性的前提下,赶上并超过RISC微处理器的。如上所述,586系列微处理器并非是CISC体系结构80386/486的延伸,而是采用了R1SC体系结构型的整数处理部件(CPU)。这样,586不仅可以充分利用RISC体系结构微处理器的软件资源,而且增强了586的软件资源,因而增强了586的市场竞争力。